ઈલેક્ટ્રોનિક આઈસી ચિપ સપોર્ટ BOM સર્વિસ TPS54560BDDAR તદ્દન નવી આઈસી ચિપ્સ ઈલેક્ટ્રોનિક્સ ઘટકો

ઉત્પાદન વિશેષતાઓ

| TYPE | વર્ણન |

| શ્રેણી | સંકલિત સર્કિટ (ICs) |

| Mfr | ટેક્સાસ ઇન્સ્ટ્રુમેન્ટ્સ |

| શ્રેણી | ઇકો-મોડ™ |

| પેકેજ | ટેપ અને રીલ (TR) કટ ટેપ (CT) ડિજી-રીલ® |

| SPQ | 2500T&R |

| ઉત્પાદન સ્થિતિ | સક્રિય |

| કાર્ય | નીચે ઉતારો |

| આઉટપુટ રૂપરેખાંકન | હકારાત્મક |

| ટોપોલોજી | બક, સ્પ્લિટ રેલ |

| આઉટપુટ પ્રકાર | એડજસ્ટેબલ |

| આઉટપુટની સંખ્યા | 1 |

| વોલ્ટેજ - ઇનપુટ (ન્યૂનતમ) | 4.5 વી |

| વોલ્ટેજ - ઇનપુટ (મહત્તમ) | 60 વી |

| વોલ્ટેજ - આઉટપુટ (મિનિટ/નિયત) | 0.8 વી |

| વોલ્ટેજ - આઉટપુટ (મહત્તમ) | 58.8V |

| વર્તમાન - આઉટપુટ | 5A |

| આવર્તન - સ્વિચિંગ | 500kHz |

| સિંક્રનસ રેક્ટિફાયર | No |

| ઓપરેટિંગ તાપમાન | -40°C ~ 150°C (TJ) |

| માઉન્ટિંગ પ્રકાર | સપાટી માઉન્ટ |

| પેકેજ / કેસ | 8-PowerSOIC (0.154", 3.90mm પહોળાઈ) |

| સપ્લાયર ઉપકરણ પેકેજ | 8-SO પાવરપેડ |

| બેઝ પ્રોડક્ટ નંબર | TPS54560 |

1.IC નામકરણ, પેકેજ સામાન્ય જ્ઞાન અને નામકરણ નિયમો:

તાપમાન ની હદ.

C=0°C થી 60°C (વાણિજ્યિક ગ્રેડ);I=-20°C થી 85°C (ઔદ્યોગિક ગ્રેડ);E=-40°C થી 85°C (વિસ્તૃત ઔદ્યોગિક ગ્રેડ);A=-40°C થી 82°C (એરોસ્પેસ ગ્રેડ);M=-55°C થી 125°C (લશ્કરી ગ્રેડ)

પેકેજ પ્રકાર.

A-SSOP;B-CERQUAD;C-TO-200, TQFP;ડી-સિરામિક કોપર ટોપ;ઇ-ક્યુએસઓપી;એફ-સિરામિક એસઓપી;H- SBGAJ-સિરામિક DIP;K-TO-3;L-LCC, M-MQFP;N- સાંકડી ડીઆઈપી;એન-ડીઆઈપી;Q PLCC;આર - સાંકડી સિરામિક DIP (300mil);S - TO-52, T - TO5, TO-99, TO-100;U - TSSOP, uMAX, SOT;W - વાઈડ સ્મોલ ફોર્મ ફેક્ટર (300mil) W-વાઇડ સ્મોલ ફોર્મ ફેક્ટર (300 mil);X-SC-60 (3P, 5P, 6P);Y- સાંકડી કોપર ટોપ;Z-TO-92, MQUAD;ડી-ડાઇ;/PR-પ્રબલિત પ્લાસ્ટિક;/W-વેફર.

પિનની સંખ્યા:

a-8;b-10;c-12, 192;ડી-14;e-16;f-22, 256;g-4;h-4;i -4;H-4;I-28;જે-2;K-5, 68;એલ -40;એમ-6, 48;એન 18;ઓ-42;પી -20;પ્રશ્ન-2, 100;આર-3, 843;એસ-4, 80;ટી-6, 160;U-60 -6,160;U-60;વી -8 (રાઉન્ડ);W-10 (રાઉન્ડ);X-36;Y-8 (રાઉન્ડ);Z-10 (રાઉન્ડ).(ગોળ)

નોંધ: ઇન્ટરફેસ વર્ગના ચાર અક્ષરના પ્રત્યયનો પ્રથમ અક્ષર E છે, જેનો અર્થ છે કે ઉપકરણમાં એન્ટિસ્ટેટિક કાર્ય છે.

2.પેકેજીંગ ટેકનોલોજીનો વિકાસ

પ્રારંભિક સંકલિત સર્કિટમાં સિરામિક ફ્લેટ પેકેજોનો ઉપયોગ થતો હતો, જે તેમની વિશ્વસનીયતા અને નાના કદને કારણે ઘણા વર્ષો સુધી લશ્કર દ્વારા ઉપયોગમાં લેવાનું ચાલુ રાખ્યું હતું.કોમર્શિયલ સર્કિટ પેકેજિંગ ટૂંક સમયમાં સિરામિક અને પછી પ્લાસ્ટિકથી શરૂ કરીને ડ્યુઅલ ઇન-લાઇન પેકેજોમાં સ્થાનાંતરિત થયું અને 1980ના દાયકામાં VLSI સર્કિટની પિન કાઉન્ટ ડીઆઈપી પેકેજોની એપ્લિકેશન મર્યાદા કરતાં વધી ગઈ, જે આખરે પિન ગ્રીડ એરે અને ચિપ કેરિયર્સના ઉદભવ તરફ દોરી ગઈ.

સરફેસ માઉન્ટ પેકેજ 1980 ના દાયકાની શરૂઆતમાં ઉભરી આવ્યું હતું અને તે દાયકાના ઉત્તરાર્ધમાં લોકપ્રિય બન્યું હતું.તે ઝીણી પિન પિચનો ઉપયોગ કરે છે અને તેમાં ગુલ-વિંગ અથવા જે-આકારની પિન આકાર હોય છે.સ્મોલ-આઉટલાઇન ઇન્ટિગ્રેટેડ સર્કિટ (SOIC), ઉદાહરણ તરીકે, 30-50% ઓછો વિસ્તાર ધરાવે છે અને સમકક્ષ DIP કરતાં 70% ઓછી જાડાઈ ધરાવે છે.આ પેકેજમાં ગલ-પાંખ આકારની પિન બે લાંબી બાજુઓમાંથી બહાર નીકળેલી છે અને પિન 0.05" છે.

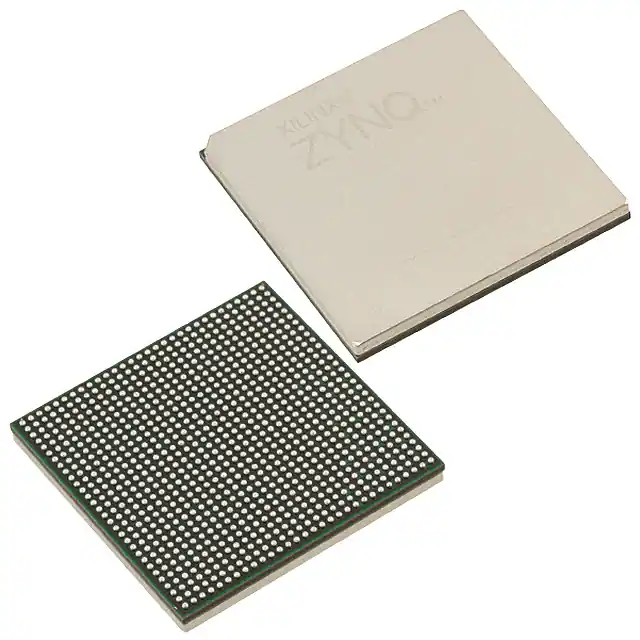

સ્મોલ-આઉટલાઇન ઇન્ટિગ્રેટેડ સર્કિટ (SOIC) અને PLCC પેકેજો.1990 ના દાયકામાં, જોકે પીજીએ પેકેજ હજુ પણ ઉચ્ચ-અંતિમ માઇક્રોપ્રોસેસર્સ માટે ઉપયોગમાં લેવાતું હતું.PQFP અને પાતળું સ્મોલ-આઉટલાઇન પેકેજ (TSOP) ઉચ્ચ પિન કાઉન્ટ ઉપકરણો માટે સામાન્ય પેકેજ બની ગયું છે.ઇન્ટેલ અને એએમડીના હાઇ-એન્ડ માઇક્રોપ્રોસેસર્સ પીજીએ (પાઇન ગ્રીડ એરે) પેકેજોમાંથી લેન્ડ ગ્રીડ એરે (એલજીએ) પેકેજોમાં ખસેડાયા છે.

બોલ ગ્રીડ એરે પેકેજો 1970 ના દાયકામાં દેખાવાનું શરૂ થયું, અને 1990 ના દાયકામાં FCBGA પેકેજ અન્ય પેકેજો કરતાં વધુ પિન કાઉન્ટ સાથે વિકસાવવામાં આવ્યું.FCBGA પેકેજમાં, ડાઇને ઉપર-નીચે ફ્લિપ કરવામાં આવે છે અને વાયરને બદલે PCB જેવા બેઝ લેયર દ્વારા પેકેજ પર સોલ્ડર બોલ્સ સાથે જોડવામાં આવે છે.આજના બજારમાં, પેકેજિંગ પણ હવે પ્રક્રિયાનો એક અલગ ભાગ છે, અને પેકેજની તકનીક ઉત્પાદનની ગુણવત્તા અને ઉપજને પણ અસર કરી શકે છે.