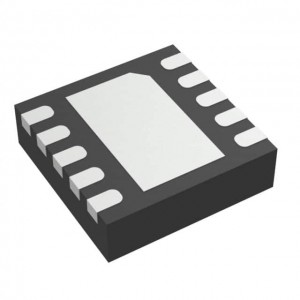

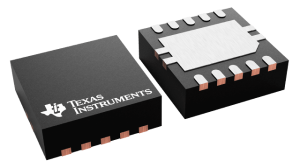

સેમિકોન માઇક્રોકન્ટ્રોલર વોલ્ટેજ રેગ્યુલેટર IC ચિપ્સ TPS62420DRCR SON10 ઇલેક્ટ્રોનિક ઘટકો BOM સૂચિ સેવા

ઉત્પાદન વિશેષતાઓ

| TYPE | વર્ણન |

| શ્રેણી | સંકલિત સર્કિટ (ICs) |

| Mfr | ટેક્સાસ ઇન્સ્ટ્રુમેન્ટ્સ |

| શ્રેણી | - |

| પેકેજ | ટેપ અને રીલ (TR) કટ ટેપ (CT) ડિજી-રીલ® |

| SPQ | 3000T&R |

| ઉત્પાદન સ્થિતિ | સક્રિય |

| કાર્ય | નીચે ઉતારો |

| આઉટપુટ રૂપરેખાંકન | હકારાત્મક |

| ટોપોલોજી | બક |

| આઉટપુટ પ્રકાર | એડજસ્ટેબલ |

| આઉટપુટની સંખ્યા | 2 |

| વોલ્ટેજ - ઇનપુટ (ન્યૂનતમ) | 2.5 વી |

| વોલ્ટેજ - ઇનપુટ (મહત્તમ) | 6V |

| વોલ્ટેજ - આઉટપુટ (મિનિટ/નિયત) | 0.6 વી |

| વોલ્ટેજ - આઉટપુટ (મહત્તમ) | 6V |

| વર્તમાન - આઉટપુટ | 600mA, 1A |

| આવર્તન - સ્વિચિંગ | 2.25MHz |

| સિંક્રનસ રેક્ટિફાયર | હા |

| ઓપરેટિંગ તાપમાન | -40°C ~ 85°C (TA) |

| માઉન્ટિંગ પ્રકાર | સપાટી માઉન્ટ |

| પેકેજ / કેસ | 10-VFDFN એક્સપોઝ્ડ પેડ |

| સપ્લાયર ઉપકરણ પેકેજ | 10-VSON (3x3) |

| બેઝ પ્રોડક્ટ નંબર | TPS62420 |

પેકેજિંગ ખ્યાલ:

સંકુચિત અર્થ: ફિલ્મ ટેકનોલોજી અને માઇક્રોફેબ્રિકેશન તકનીકોનો ઉપયોગ કરીને ફ્રેમ અથવા સબસ્ટ્રેટ પર ચિપ્સ અને અન્ય ઘટકોને ગોઠવવાની, જોડવાની અને જોડવાની પ્રક્રિયા, જે ટર્મિનલ્સ તરફ દોરી જાય છે અને એકંદર ત્રિ-પરિમાણીય માળખું રચવા માટે નમ્ર અવાહક માધ્યમથી પોટ કરીને તેમને ઠીક કરે છે.

વ્યાપક રીતે કહીએ તો: સબસ્ટ્રેટ સાથે પેકેજને કનેક્ટ કરવાની અને તેને ઠીક કરવાની પ્રક્રિયા, તેને સંપૂર્ણ સિસ્ટમ અથવા ઇલેક્ટ્રોનિક ઉપકરણમાં એસેમ્બલ કરવાની અને સમગ્ર સિસ્ટમના વ્યાપક પ્રદર્શનને સુનિશ્ચિત કરવાની પ્રક્રિયા.

ચિપ પેકેજિંગ દ્વારા પ્રાપ્ત કાર્યો.

1. ટ્રાન્સફર ફંક્શન્સ;2. સર્કિટ સિગ્નલોનું પરિવહન;3. ગરમીના વિસર્જનનું સાધન પૂરું પાડવું;4. માળખાકીય રક્ષણ અને આધાર.

પેકેજિંગ એન્જિનિયરિંગનું તકનીકી સ્તર.

IC ચિપ બનાવ્યા પછી પેકેજિંગ એન્જિનિયરિંગ શરૂ થાય છે અને તેમાં IC ચિપ પેસ્ટ અને ફિક્સ થાય તે પહેલાંની તમામ પ્રક્રિયાઓનો સમાવેશ થાય છે, ઇન્ટરકનેક્ટેડ, એન્કેપ્સ્યુલેટેડ, સીલબંધ અને સુરક્ષિત, સર્કિટ બોર્ડ સાથે જોડાયેલ અને અંતિમ ઉત્પાદન પૂર્ણ થાય ત્યાં સુધી સિસ્ટમ એસેમ્બલ થાય છે.

પ્રથમ સ્તર: ચિપ લેવલ પેકેજિંગ તરીકે પણ ઓળખાય છે, તે પેકેજિંગ સબસ્ટ્રેટ અથવા લીડ ફ્રેમમાં IC ચિપને ફિક્સિંગ, ઇન્ટરકનેક્ટિંગ અને સુરક્ષિત કરવાની પ્રક્રિયા છે, જે તેને મોડ્યુલ (એસેમ્બલી) ઘટક બનાવે છે જેને સરળતાથી ઉપાડી શકાય છે અને પરિવહન અને કનેક્ટ કરી શકાય છે. એસેમ્બલીના આગલા સ્તર પર.

સ્તર 2: સર્કિટ કાર્ડ બનાવવા માટે અન્ય ઇલેક્ટ્રોનિક ઘટકો સાથે સ્તર 1 ના ઘણા પેકેજોને સંયોજિત કરવાની પ્રક્રિયા.સ્તર 3: મુખ્ય બોર્ડ પર એક ઘટક અથવા સબસિસ્ટમ બનાવવા માટે સ્તર 2 પર પૂર્ણ થયેલા પેકેજોમાંથી એસેમ્બલ કરાયેલા કેટલાક સર્કિટ કાર્ડ્સને જોડવાની પ્રક્રિયા.

સ્તર 4: સંપૂર્ણ ઈલેક્ટ્રોનિક પ્રોડક્ટમાં અનેક સબસિસ્ટમને એસેમ્બલ કરવાની પ્રક્રિયા.

ચિપમાં.ચિપ પર ઇન્ટિગ્રેટેડ સર્કિટ ઘટકોને જોડવાની પ્રક્રિયાને શૂન્ય-સ્તરના પેકેજિંગ તરીકે પણ ઓળખવામાં આવે છે, તેથી પેકેજિંગ એન્જિનિયરિંગને પાંચ સ્તરોથી પણ ઓળખી શકાય છે.

પેકેજોનું વર્ગીકરણ:

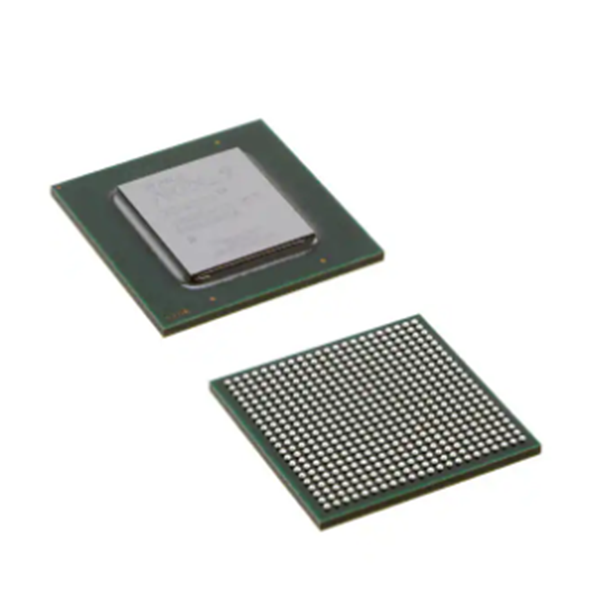

1, પેકેજમાં IC ચિપ્સની સંખ્યા અનુસાર: સિંગલ ચિપ પેકેજ (SCP) અને મલ્ટી-ચિપ પેકેજ (MCP).

2, સીલિંગ સામગ્રીના તફાવત અનુસાર: પોલિમર સામગ્રી (પ્લાસ્ટિક) અને સિરામિક્સ.

3, ઉપકરણ અને સર્કિટ બોર્ડ ઇન્ટરકનેક્શન મોડ અનુસાર: પિન દાખલ પ્રકાર (PTH) અને સરફેસ માઉન્ટ પ્રકાર (SMT) 4, પિન વિતરણ ફોર્મ અનુસાર: સિંગલ-સાઇડ પિન, ડબલ-સાઇડ પિન, ફોર-સાઇડ પિન અને તળિયે પિન.

એસએમટી ઉપકરણોમાં એલ-ટાઈપ, જે-ટાઈપ અને આઈ-ટાઈપ મેટલ પિન હોય છે.

SIP: સિંગલ-રો પેકેજ SQP: લઘુચિત્ર પેકેજ MCP: મેટલ પોટ પેકેજ DIP: ડબલ-રો પેકેજ CSP: ચિપ કદ પેકેજ QFP: ક્વોડ-સાઇડ ફ્લેટ પેકેજ PGA: ડોટ મેટ્રિક્સ પેકેજ BGA: બોલ ગ્રીડ એરે પેકેજ LCCC: લીડલેસ સિરામિક ચિપ કેરિયર